Atlys

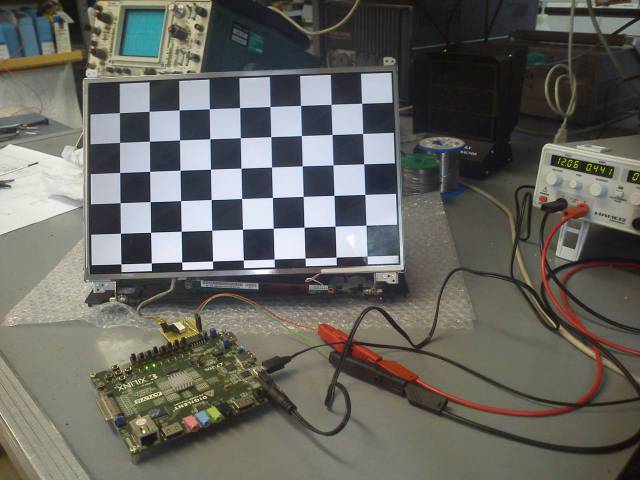

Auch mit programmierbarer Logik beschäftigen wir uns. Aktuelle FPGAs erlauben beeindruckende Experimente auch mit hochauflösendem Video.

Technische Daten

Atlys ist eine FPGA Platine der Firma Digilent. Sie ist bestueckt mit einem Spartan-6 LX45 FPGA, je 2 HDMI Ein- und Ausgaengen, Gigabit Ethernet und einem Audio-Codec. Ein 400MHz DDR2 Ram sorgt fuer reichlich Speicherbandbreite.

Der Spartan-6 beherrscht TMDS als IO-Standard und kann damit DVI/HDMI bis 720p/1080i direkt auf dem Chip erzeugen oder empfangen (Datenrate bei 720p ca. 1280 * 720 Pixel * 60 Hz * 32 Bit/Pixel = 1,8 GBit/s = 221 MByte/s). Zum Vergleich: Die Spitzen-Speicherbandbreite des DDR2 RAMs beträgt 400 MHz * 2 Zugriffe je Takt * 16 Bit/Zugriff = 12,8 GBit/s = 1,6 GByte/s („Spitze“, da der Wert durch Adressierungs-Overhead, Refresh, etc. nicht dauerhaft zu halten ist).

Adept EPP

Digilent hat für seine Adept Software ein standardisiertes Interface entwickelt, das es erlaubt 8-Bit Register im FPGA zu implementieren und direkt über die Adept Software darauf zu schreiben und zu lesen. Leider sind im Reference Manual die benötigten Pins nicht dokumentiert, hier ein zum Beispielcode dpimref.vhd passendes UCF-File. Es sind kleine Anpassungen am VHDL-Code nötig um die Datei verwenden zu können.

- dpimref.ucf

############################################################### # UCF for Digilent dpimref.vhd # for use with Atlys board, XC6SLX45-2CSG324 FPGA ############################################################### NET "pdb[0]" IOSTANDARD = LVCMOS25 | LOC = "A2"; # Schematic name: U1-FD0 NET "pdb[1]" IOSTANDARD = LVCMOS25 | LOC = "D6"; # Schematic name: U1-FD1 NET "pdb[2]" IOSTANDARD = LVCMOS25 | LOC = "C6"; # Schematic name: U1-FD2 NET "pdb[3]" IOSTANDARD = LVCMOS25 | LOC = "B3"; # Schematic name: U1-FD3 NET "pdb[4]" IOSTANDARD = LVCMOS25 | LOC = "A3"; # Schematic name: U1-FD4 NET "pdb[5]" IOSTANDARD = LVCMOS25 | LOC = "B4"; # Schematic name: U1-FD5 NET "pdb[6]" IOSTANDARD = LVCMOS25 | LOC = "A4"; # Schematic name: U1-FD6 NET "pdb[7]" IOSTANDARD = LVCMOS25 | LOC = "C5"; # Schematic name: U1-FD7 NET "astb" IOSTANDARD = LVCMOS25 | LOC = "B9"; # Schematic name: U1-FLAGA NET "dstb" IOSTANDARD = LVCMOS25 | LOC = "A9"; # Schematic name: U1-FLAGB NET "pwr" IOSTANDARD = LVCMOS25 | LOC = "C15"; # Schematic name: U1-FLAGC NET "pwait" IOSTANDARD = LVCMOS25 | LOC = "F13"; # Schematic name: U1-SLRD NET "rgLed[0]" IOSTANDARD = LVCMOS25 | LOC = "U18"; # Schematic name: LD0 NET "rgLed[1]" IOSTANDARD = LVCMOS25 | LOC = "M14"; # Schematic name: LD1 NET "rgLed[2]" IOSTANDARD = LVCMOS25 | LOC = "N14"; # Schematic name: LD2 NET "rgLed[3]" IOSTANDARD = LVCMOS25 | LOC = "L14"; # Schematic name: LD3 NET "rgLed[4]" IOSTANDARD = LVCMOS25 | LOC = "M13"; # Schematic name: LD4 NET "rgLed[5]" IOSTANDARD = LVCMOS25 | LOC = "D4"; # Schematic name: LD5 NET "rgLed[6]" IOSTANDARD = LVCMOS25 | LOC = "P16"; # Schematic name: LD6 NET "rgLed[7]" IOSTANDARD = LVCMOS25 | LOC = "N12"; # Schematic name: LD7 NET "rgSwt[0]" IOSTANDARD = LVCMOS25 | LOC = "A10"; # Schematic name: SW0 NET "rgSwt[1]" IOSTANDARD = LVCMOS25 | LOC = "D14"; # Schematic name: SW1 NET "rgSwt[2]" IOSTANDARD = LVCMOS25 | LOC = "C14"; # Schematic name: SW2 NET "rgSwt[3]" IOSTANDARD = LVCMOS25 | LOC = "P15"; # Schematic name: SW3 NET "rgSwt[4]" IOSTANDARD = LVCMOS25 | LOC = "P12"; # Schematic name: SW4 NET "rgSwt[5]" IOSTANDARD = LVCMOS25 | LOC = "R5"; # Schematic name: SW5 NET "rgSwt[6]" IOSTANDARD = LVCMOS25 | LOC = "T5"; # Schematic name: SW6 NET "rgSwt[7]" IOSTANDARD = LVCMOS25 | LOC = "E4"; # Schematic name: SW7 NET "rgBtn[0]" IOSTANDARD = LVCMOS25 | LOC = "N4"; # Schematic name: BTNU NET "rgBtn[1]" IOSTANDARD = LVCMOS25 | LOC = "F5"; # Schematic name: BTNC NET "rgBtn[2]" IOSTANDARD = LVCMOS25 | LOC = "F6"; # Schematic name: BTNR NET "rgBtn[3]" IOSTANDARD = LVCMOS25 | LOC = "P4"; # Schematic name: BTNL NET "rgBtn[4]" IOSTANDARD = LVCMOS25 | LOC = "P3"; # Schematic name: BTND NET "rgBtn[5]" IOSTANDARD = LVCMOS25 | LOC = "T15"; # Schematic name: BRST # btn, led, ldg removed

TFT-Panel mit LVDS

In allen Laptops der letzten Jahre sind TFT-Panels mit LVDS-Interface verbaut. Dabei handelt es sich um eine eine schnelle serielle Datenübertragung mit differenziellen Signalen. Die meisten Panels können 18-bit Farben darstellen (je 6-Bit für rot, grün und blau) und werden über 4 LVDS-Paare angesteuert: 3 Paare für die Pixeldaten sowie Synchronisationssignale und ein Paar für den Pixeltakt.

Für unsere Tests wurde das WSXGA (1280×800) Panel LTN154X3-L06 verwendet. Im Datenblatt findet sich neben der Pinbelegung auch die benötigte Bitanordnung auf den einzelnen LVDS-Kannälen sowie die Phase des Pixeltaktsignals. Hier sind die Informationen noch einmal zusammengefasst:

| Bit | Verwendung |

|---|---|

| 0 | ROT 0 |

| 1 | ROT 1 |

| 2 | ROT 2 |

| 3 | ROT 3 |

| 4 | ROT 4 |

| 5 | ROT 5 |

| 6 | GRÜN 0 |

| 7 | GRÜN 1 |

| 8 | GRÜN 2 |

| 9 | GRÜN 3 |

| 10 | GRÜN 4 |

| 11 | GRÜN 5 |

| 12 | BLAU 0 |

| 13 | BLAU 1 |

| 14 | BLAU 2 |

| 15 | BLAU 3 |

| 16 | BLAU 4 |

| 17 | BLAU 5 |

| 18 | HSYNC |

| 19 | VSYNC |

| 20 | VDE |

Je 7 Bit werden dabei in einen LVDS-Kanal serialisiert:

| LVDS Kanal | Timeslot 0 | Timeslot 1 | Timeslot 2 | Timeslot 3 | Timeslot 4 | Timeslot 5 | Timeslot 6 |

|---|---|---|---|---|---|---|---|

| TX 0 | G0 | R5 | R4 | R3 | R2 | R1 | R0 |

| TX 1 | B1 | B0 | G5 | G4 | G3 | G2 | G1 |

| TX 2 | VDE | HSYNC | VSYNC | B5 | B4 | B3 | B2 |

| TXCLK | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

HSYNC und VSYNC sind die aus bei VGA-Signales üblichen Synchronisationspulse mit negativer Polarität, VDE (video data enable) ist im sichtbaren Breeich jeder Videozeile aktiv. Um das TFT-Panel anzusteuern sind neben einem VGA-Timinggenerator und Pixelgenerator eigentlich nur noch der Serialisierer für die LVDS-Signale und eine Taktverteilung nötig.

TODO:

- Blockschaltbild

- Beispielprojekt (Copyright!)

- Adapterplatine, Pinout Atlys

Dokumentation

Digilent

Xilinx

Sonstige

- Marvell 88e1111 Gigabit Ethernet PHY - eine Google-Suche nach „88e1111 marvell nda“ sollte einige Hinweise bringen.